- Cortex-R4

Cortex-R4

简介

Cortex™-R4 专用于大容量深层嵌入式片上系统应用,如硬盘驱动器控制器、无线基带处理器、消费性产品、手机MTK平台和汽车系统的电子控制单元。

Cortex-R4 提供的性能、实时响应性大大高于同类中的其他处理器,它提供的功能也远远多于同类中的其他处理器。此处理器为 ASIC、ASSP 和 MCU 嵌入式应用提供出色的能效和成本效益。并且,可以在合成时配置 Cortex-R4 处理器以优化其功能集以便精确匹配应用需求。

性能

Cortex-R4 是成熟的处理器,于 2006 年 5 月投放市场,如今已在数百万的 ASIC、ASSP 和 MCU 设备中使用。它是高性能实时 SoC 的标准,取代了许多基于 ARM9 和 ARM11 处理器的设计。

Cortex-R4 是为基于 90 nm 至 28 nm 的高级芯片工艺的实现而设计的,此外其设计重点在于提升能效、实时响应性、高级功能和使得系统设计更加容易。基于 40 nm G 工艺,Cortex-R4 可以实现以将近 1 GHz 的频率运行,此时它可提供 1,500 Dhrystone MIPS 的性能。该处理器提供高度灵活且有效的双周期本地内存接口,使 SoC 设计者可以最大限度地降低系统成本和功耗。

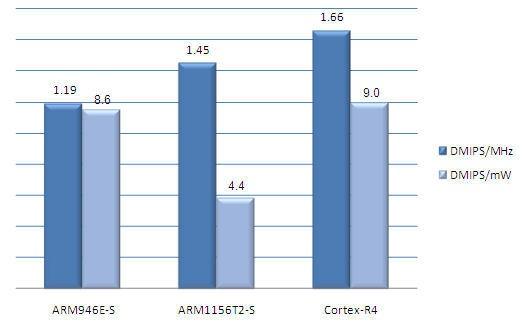

图1对基于 90 nm G 工艺实现的 Cortex-R4 与经典 ARM 处理器的 Dhrystone 基准性能进行了比较。Cortex-R4 的配置选项可以进行选择以最大限度地减少处理器的芯片面积,重要的是这还可以最大限度地降低漏泄功率。

Cortex-R4 性能更好、能效更高

图1 Cortex-R4性能

图1 Cortex-R4性能

对比

Cortex-R4 与以前的 ARM9 和 ARM11 处理器相比具有其他许多显著优势:

| 内核 | ARM946E-S | ARM1156T2-S | Cortex-R4 |

|---|---|---|---|

| 体系结构 | ARMv5TE | ARMv6T2 | ARMv7-R |

| 预取单元 | 否 | 指令预取和分支预测 | |

| 超标量执行 | 否 | 双执行指令 | |

| Thumb-2 指令 | 否 | 是 | |

| 浮点支持 | VFP9 | VFP11 | 已集成 (Cortex-R4F) |

| 总线接口 | AMBA AHB | AMBA3 AXI | |

| 紧密耦合内存 (TCM) | 基本 | 代码和数据分离 | 完全灵活 |

| 中断 | ARMv5 | ARMv6 增强功能、NMI | |

| 软错误管理 | 否 | 针对所有 RAM 的可选奇偶校验和 ECC | |

| 内存保护单元 (MPU) | 8 个区域 | 16 个区域 | 12 个区域 |

| 最小区域大小 | 4k 字节 | 32 字节,重叠区域 | |

| 合成可配置性 | 否 | I 和 D 高速缓存。0 或 2 个 TCM。软错误处理。MPU | I 和 D 高速缓存。0、1、2 或 3 个 TCM。FPU。软错误处理。MPU。AXI 从属设备 |

-

江铃福特轻客持续打造最优TCO 锐骐超值版PK江铃国产共轨

2025-11-01 11:15:17 查看详情 -

江铃福特轻客持续打造最优TCO 江铃E200N豪华型怎么样

2025-11-01 11:15:17 查看详情 -

PRO上市 售价9.48万

2025-11-01 11:15:17 查看详情 -

将于4月底上市 内外升级的不止一点

2025-11-01 11:15:17 查看详情 -

将于4月底上市 预计将于7月上市

2025-11-01 11:15:17 查看详情 -

380TSI劲擎智联版四驱车型上市 成都车展:雪铁龙C

2025-11-01 11:15:17 查看详情 -

欧拉新款R1将于成都车展上市 全新宝马2系Coupe最新谍照

2025-11-01 11:15:17 查看详情 -

2023款凯迪拉克XT4上市 奔驰A

2025-11-01 11:15:17 查看详情 -

西安大众速腾现金优惠2.3万 成都沃尔沃XC90优惠三万元

2025-11-01 11:15:17 查看详情 -

Pro将于4月15日上市 12.9万元

2025-11-01 11:15:17 查看详情

求购

求购