- CRC校验

CRC校验

工作原理

循环冗余校验码(CRC)的基本原理是:在K位信息码后再拼接R位的校验码,整个编码长度为N位,因此,这种编码也叫(N,K)码。对于一个给定的(N,K)码,可以证明存在一个最高次幂为N-K=R的多项式G(x)。根据G(x)可以生成K位信息的校验码,而G(x)叫做这个CRC码的生成多项式。 校验码的具体生成过程为:假设要发送的信息用多项式C(X)表示,将C(x)左移R位(可表示成C(x)*2R),这样C(x)的右边就会空出R位,这就是校验码的位置。用 C(x)*2R除以生成多项式G(x)得到的余数就是校验码。

循环冗余校验码(CRC)的基本原理是:在K位信息码后再拼接R位的校验码,整个编码长度为N位,因此,这种编码也叫(N,K)码。对于一个给定的(N,K)码,可以证明存在一个最高次幂为N-K=R的多项式G(x)。根据G(x)可以生成K位信息的校验码,而G(x)叫做这个CRC码的生成多项式。 校验码的具体生成过程为:假设要发送的信息用多项式C(X)表示,将C(x)左移R位(可表示成C(x)*2R),这样C(x)的右边就会空出R位,这就是校验码的位置。用 C(x)*2R除以生成多项式G(x)得到的余数就是校验码。

任意一个由二进制位串组成的代码都可以和一个系数仅为‘0’和‘1’取值的多项式一一对应。例如:代码1010111对应的多项式为x6+x4+x2+x+1,而多项式为x5+x3+x2+x+1对应的代码101111。

基本概念

对应关系

CRC校验(3)多项式和二进制数有直接对应关系:X的最高幂次对应二进制数的最高位,以下各位对应多项式的各幂次,有此幂次项对应1,无此幂次项对应0。可以看出:X的最高幂次为R,转换成对应的二进制数有R+1位。

CRC校验(3)多项式和二进制数有直接对应关系:X的最高幂次对应二进制数的最高位,以下各位对应多项式的各幂次,有此幂次项对应1,无此幂次项对应0。可以看出:X的最高幂次为R,转换成对应的二进制数有R+1位。

多项式包括生成多项式G(X)和信息多项式C(X)。

如生成多项式为G(X)=X4+X3+X+1, 可转换为二进制数码11011。

而发送信息位 101111,可转换为数据多项式为C(X)=X5+X3+X2+X+1。

生成多项式

是接受方和发送方的一个约定,也就是一个二进制数,在整个传输过程中,这个数始终保持不变。

在发送方,利用生成多项式对信息多项式做模2除生成校验码。在接收方利用生成多项式对收到的编码多项式做模2除检测和确定错误位置。

应满足以下条件:

A、生成多项式的最高位和最低位必须为1。

B、当被传送信息(CRC码)任何一位发生错误时,被生成多项式做除后应该使余数不为0。

C、不同位发生错误时,应该使余数不同。

D、对余数继续做除,应使余数循环。

校验码位数

CRC校验码位数 = 生成多项式位数 - 1。注意有些生成多项式的简记式中将生成多项式的最高位1省略了。

生成步骤

1、将X的最高次幂为R的生成多项式G(X)转换成对应的R+1位二进制数。

2、将信息码左移R位,相当于对应的信息多项式C(X)*2R。

3、用生成多项式(二进制数)对信息码做除,得到R位的余数(注意:这里的二进制做除法得到的余数其实是模2除法得到的余数,并不等于其对应十进制数做除法得到的余数。)。

4、将余数拼到信息码左移后空出的位置,得到完整的CRC码。

【例】假设使用的生成多项式是G(X)=X3+X+1。4位的原始报文为1010,求编码后的报文。

解:

1、将生成多项式G(X)=X3+X+1转换成对应的二进制除数1011。

2、此题生成多项式有4位(R+1)(注意:4位的生成多项式计算所得的校验码为3位,R为校验码位数),要把原始报文C(X)左移3(R)位变成1010 000

3、用生成多项式对应的二进制数对左移3位后的原始报文进行模2除(高位对齐),相当于按位异或:

1010000

1011

------------------

0001000

0001011

------------------

0000011

得到的余位011,所以最终编码为:1010 011

原则

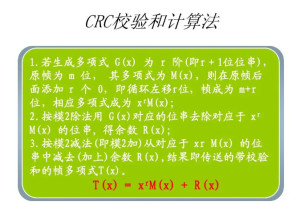

若设码字长度为N,信息字段为K位,校验字段为R位(N=K+R),则对于CRC码集中的任一码字,存在且仅存在一个R次多项式g(x),使得

V(x)=A(x)g(x)=xRm(x)+r(x);

其中: m(x)为K次原始的信息多项式, r(x)为R-1次校验多项式(即CRC校验和),

g(x)称为生成多项式:

g(x)=g0+g1x1+ g2x2+...+g(R-1)x(R-1)+gRxR

发送方通过指定的g(x)产生CRC码字,接收方则通过该g(x)来验证收到的CRC码字。

生成方法

借助于模2除法则,其余数为校验字段。

例如:信息字段代码为: 1011001;对应m(x)=x6+x4+x3+1

假设生成多项式为:g(x)=x4+x3+1;则对应g(x)的代码为: 11001

x4m(x)=x10+x8+x7+x4对应的代码记为:10110010000;

采用模2除法则: 得余数为: 1010(即校验字段为:1010)

发送方:发出的传输字段为: 1 0 1 1 0 0 1 1010

信息字段 校验字段

接收方:使用相同的生成码进行校验:接收到的字段/生成码(二进制除法)

如果能够除尽,则正确,

给出余数(1010)的计算步骤:

除法没有数学上的含义,而是采用计算机的模二除法,即除数和被除数做异或运算。进行异或运算时除数和被除数最高位对齐,按位异或。

10110010000

^11001

--------------------------

01111010000

1111010000

^11001

-------------------------

0011110000

11110000

^11001

--------------------------

00111000

111000

^11001

-------------------

001010

则四位CRC校验码就为:1010。

利用CRC进行检错的过程可简单描述为:在发送端根据要传送的k位二进制码序列,以一定的规则产生一个校验用的r位监督码(CRC码),附在原始信息后边,构成一个新的二进制码序列数共k+r位,然后发送出去。在接收端,根据信息码和CRC码之间所遵循的规则进行检验,以确定传送中是否出错。这个规则,在差错控制理论中称为“生成多项式”。

算法

在代数编码理论中,将一个码组表示为一个多项式,码组中各码元当作多项式的系数。例如 1100101 表示为1·x[2]

名称 生成多项式 简记式* 应用举例

CRC-4 x4+x+1 3 ITU G.704

CRC-8 x8+x5+x4+1 31 DS18B20

CRC-12 x12+x11+x3+x2+x+1 80F

CRC-16 x16+x15+x2+1 8005 IBM SDLC

CRC-ITU** x16+x12+x5+1 1021 ISO HDLC, ITU X.25, V.34/V.41/V.42, PPP-FCS,ZigBee

CRC-32 x32+x26+x23+...+x2+x+1 04C11DB7 ZIP, RAR, IEEE 802 LAN/FDDI,IEEE 1394,PPP-FCS

CRC-32c x32+x28+x27+...+x8+x6+1 1EDC6F41 SCTP

* 生成多项式的最高幂次项系数是固定的1,故在简记式中,将最高的1统一去掉了,如04C11DB7实际上是104C11DB7。 ** 前称CRC-CCITT。ITU的前身是CCITT。

备注:

(1)生成多项式是标准规定的

(2)CRC校验码是基于将位串看作是系数为0或1的多项式,一个k位的数据流可以看作是关于x的从k-1阶到0阶的k-1次多项式的系数序列。采用此编码,发送方和接收方必须事先商定一个生成多项式G(x),其高位和低位必须是1。要计算m位的帧M(x)的校验和,基本思想是将校验和加在帧的末尾,使这个带校验和的帧的多项式能被G(x)除尽。当接收方收到加有校验和的帧时,用G(x)去除它,如果有余数,则CRC校验错误,只有没有余数的校验才是正确的。[3]

校验电路实现

以下以CRC8x8+x5+x4+1为例说明,其它可以以此类推

生成算法

一个简单的RTL解释,是上文“生成方法”的Verilog描述

module CRC8(EN,data,crc);

parameter WIDTH=12;

input EN;

output[7:0]crc;

input[WIDTH-1:0]data;

reg[7:0]crc;

wire[7:0]poly=8'h31;//x8+x5+x4+1-->0x131,ignore MSB

reg[WIDTH-1+8:0]crc_reg;

integer len;

always@(EN)

begin

if(!EN)

begin

crc=8'h00;

crc_reg={data,8'h00};

end

else

begin

for(len=WIDTH+8;len>0;len=len-1'b1)

begin

if(crc_reg[WIDTH-1+8])

begin

crc_reg[WIDTH-1+8:WIDTH]=crc_reg[WIDTH-1+8:WIDTH]^poly;

crc_reg=crc_reg<<1'b1;

end

else

crc_reg=crc_reg<<1'b1;

end

crc=crc_reg[WIDTH-1+8:WIDTH];

$display("Convertion done! CRC is: 0x%2x",crc);

end

end

endmodule

检测电路

![]() CRC-8的电路框图

CRC-8的电路框图

module crc(dataout,datain,clk,rst);

input clk,rst,datain;

output dataout;

DFF a1(clk,dataout,Q7,rst),

a2(clk,Q7,Q6,rst),

a3(clk,Q6,Q5,rst),

a4(clk,Q5,Q4,rst);

xor a5(temp5,Q4,dataout);

DFF a6(clk,temp5,Q3,rst);

xor a7(temp4,Q3,dataout);

DFF a8(clk,temp4,Q2,rst),

a9(clk,Q2,Q1,rst),

a10(clk,Q1,Q0,rst);

xor a11(dataout,Q0,datain);

endmodule

////////////////////////////////////////

module DFF(clk,D,Q,rst);

input clk,D,rst;

output Q;

![]() Verilog简单测试reg Q;

Verilog简单测试reg Q;

always@(posedge clk or posedge rst)

begin

if(rst)

Q<=0;

else

Q<=D;

end

endmodule

-

江铃福特轻客持续打造最优TCO 锐骐超值版PK江铃国产共轨

2025-09-22 03:12:48 查看详情 -

江铃福特轻客持续打造最优TCO 江铃E200N豪华型怎么样

2025-09-22 03:12:48 查看详情 -

380TSI劲擎智联版四驱车型上市 成都车展:雪铁龙C

2025-09-22 03:12:48 查看详情 -

西安大众速腾现金优惠2.3万 成都沃尔沃XC90优惠三万元

2025-09-22 03:12:48 查看详情 -

欧拉新款R1将于成都车展上市 全新宝马2系Coupe最新谍照

2025-09-22 03:12:48 查看详情 -

将于上海车展上市 Ocean曝光

2025-09-22 03:12:48 查看详情 -

保时捷Taycan国内上市 55周年纪念版上市

2025-09-22 03:12:48 查看详情 -

哈尔滨沃尔沃XC40优惠达4.7万 优惠7万元

2025-09-22 03:12:48 查看详情 -

Face家族设计/或年内上市 各限量500台

2025-09-22 03:12:48 查看详情 -

凯迪拉克CT6新车型上市 W帅气亮相

2025-09-22 03:12:48 查看详情

求购

求购