- 非门

非门

基本功能

实现逻辑代数非的功能,即输出始终和输入保持相反。当输入端为高电平(逻辑“1”)时,输出端为低电平(逻辑“0”);反之,当输入端为低电平(逻辑“0”)时,输出端则为高电平(逻辑“1”)[1]。非门的数学逻辑表达式为:F=![]() ,其真值表如下所示[2]:

,其真值表如下所示[2]:

| 输入A | 输出Y |

|---|---|

| 0 | 1 |

| 1 | 0 |

逻辑符号

| 输入A | 输出Y |

|---|---|

| 0 | 1 |

| 1 | 0 |

实现方法

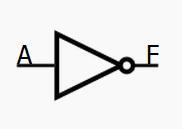

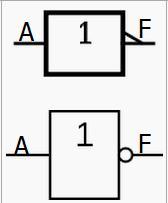

非门共有3种逻辑符号:形状特征型符号(ANSI/IEEEStd 91-1984)、IEC矩形国标符号(IEC 60617-12)和DIN符号(DIN 40700),分别如下图所示:

|

|

|

| 形状特征型符号(ANSI/IEEEStd 91-1984) | IEC矩形国标符号(IEC 60617-12) | DIN符号(DIN 40700) |

CMOS逻辑

|

|

|

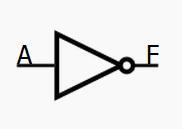

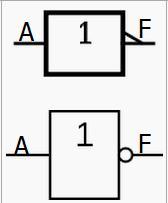

| 形状特征型符号(ANSI/IEEEStd 91-1984) | IEC矩形国标符号(IEC 60617-12) | DIN符号(DIN 40700) |

TTL逻辑

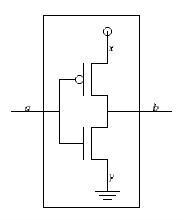

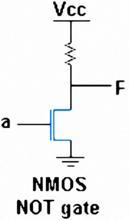

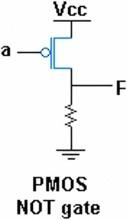

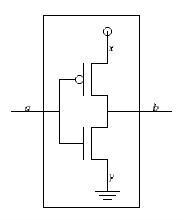

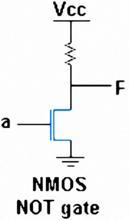

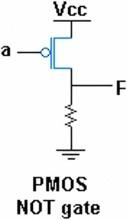

非门(反相器)通常采用CMOS逻辑和TTL逻辑,也可以通过NMOS逻辑、PMOS逻辑等来实现。

|

|

|

| CMOS反相器 | NMOS反相器 | PMOS反相器 |

集成电路

|

|

|

| CMOS反相器 | NMOS反相器 | PMOS反相器 |

词条图册

两管的栅极相连作为输入端,两管的漏极相连作为输出端。TN的源极接地,TP的源极接电源。为了保证电路正常工作,VDD需要大于TN管开启电压VTN和TP管开启电压VTP的绝对值的和,即UDD>UTN+ |UTP|。当Ui=0V时,TN截止,TP导通,Uo≈UDD为高电平;当Ui=UDD时,TN导通,TP截止,Uo≈0V为低电平。因此实现了逻辑非的功能。

相关百科

求购

求购