- 龙芯

龙芯

研发背景

据美国《华尔街日报》2015年4月9日报道,美国政府禁止企业向与世界上运算速度最快的超级计算机有关的中国设施出口技术,这对英特尔和其他硬件供应商来说是一个打击,给中美两国之间的一系列科技争端再添一项。[2]

龙芯(22)这一限令包含在美国商务部发布在联邦政府网站的一份公告中,其日期标明为2月18日,即中国除夕,但直到4月9日才有媒体获悉其存在。被列入限制名单的分别是中国国防科学技术大学、国家超级计算机长沙中心、国家超级计算机天津中心和国家超级计算机广州中心。[3]

龙芯(22)这一限令包含在美国商务部发布在联邦政府网站的一份公告中,其日期标明为2月18日,即中国除夕,但直到4月9日才有媒体获悉其存在。被列入限制名单的分别是中国国防科学技术大学、国家超级计算机长沙中心、国家超级计算机天津中心和国家超级计算机广州中心。[3]

公告声称,美国政府认定名单上的这些机构“涉及违反美国国家安全或外交政策利益的活动”。例如,“中国国防科学技术大学采用源自美国的多核、主板和处理器生产天河-1A和天河二号”,这两个系统“据信被用于核爆炸活动”。[3]

如果有美国公司要向名单上的4家中国机构出售相关技术,必须先向美国政府申请出口许可。但正如公告所指出的那样,这类许可的申请“通常会遭到政策性的拒绝”。因此这一公告实际上相当于禁令。[3]

研制课题

2001年5月,在中科院计算所知识创新工程的支持下,龙芯课题组正式成立。2002年8月10日,首片龙芯1号芯片X1A50流片成功.龙芯最初的英文名字是Godson,后来正式注册的英文名为Longstanding。龙芯CPU由中国科学院计算技术所龙芯课题组研制.由中国科学院计算技术所授权的北京神州龙芯集成电路设计公司研发,前期批量样品由台湾台积电生产。

2001年5月,在中科院计算所知识创新工程的支持下,龙芯课题组正式成立。2002年8月10日,首片龙芯1号芯片X1A50流片成功.龙芯最初的英文名字是Godson,后来正式注册的英文名为Longstanding。龙芯CPU由中国科学院计算技术所龙芯课题组研制.由中国科学院计算技术所授权的北京神州龙芯集成电路设计公司研发,前期批量样品由台湾台积电生产。

尽管的“龙芯”还存在着诸多问题与主流CPU相比性能上还有不少差距,还不能与Intel和AMD的CPU在PC市场上竞争,但坦率讲,“龙芯”的境遇已经比当年的“联想汉卡”好多了。回想当年的“联想汉卡”是由做大型机出身的毫无产业经验的科研人员一块一块的手工焊接而成、又一块一块的人工检测。据说1986年,联想第一线销售人员每天接到的投诉电话和定货电话几乎一样多----每卖出100块“汉卡”,就有30块出问题;而“龙芯”不仅获得了中科院重大知识创新工程项目和国家863计划的支持,通过了严格的成果鉴定、基准程序测试和产品测试,可进入商品化生产;还得到了各地政府和企业的大力支持,已在江苏省常熟市建立了产业化基地。关于MIPS结构授权与龙芯自主性等问题(From采访龙芯总设计师胡伟武)[4]

龙芯架构

龙芯龙芯指令集:

龙芯龙芯指令集:

CPU访存指令 24个 全部来自MIPS

CPU算数指令(ALU) 10个 全部来自MIPS

CPU算数指令 14个 全部来自MIPS

CPU乘除指令 12个 来自MIPS

12个 来自龙芯(其中8个重复MIPS指令功能)

CPU跳转分支指令20个 全部来自MIPS

CPU位移指令 15个 全部来自MIPS

CPU特殊指令 2个 全部来自MIPS

CPU异常指令 12个 全部来自MIPS

CPU CPO指令 10个 全部来自MIPS

龙芯处理器共131个指令,其中119个来自MIPS,12个来自龙芯(但其中MULTG、DMULTG、MULTUG、DMULTUG、DIVG、DDIVG、DIVUG、DDIVUG共8个重复MIPS的指令功能。)

发展历程

龙芯2001年5月,在(中国大陆)中科院计算所知识创新工程的支持下,龙芯课题组正式成立。

龙芯2001年5月,在(中国大陆)中科院计算所知识创新工程的支持下,龙芯课题组正式成立。

2001年8月19日,龙芯1号设计与验证系统成功启动linux操作系统,10月10日通过由中国科学院组织的鉴定。

2002年8月10日,首片龙芯1号龙芯XIA50流片成功。

2002年9月22日龙芯1号通过由中国科学院组织的鉴定,9月28日举行龙芯1号发布会。中国人大常委会副委员长路甬祥、全国政协副主席周光召参加了龙芯1号发布会。

2003年10月17日,龙芯2号首片MZD110流片成功。

2004年9月28日,经过多次改进后的龙芯2C芯片DXP100流片成功。

2004年11月,中国国务院总理温家宝视察中科院计算所听取龙芯研发情况汇报。

2005年2月,中国国家主席胡锦涛等党和国家领导人在参观中科院建院55周年展览时参观了龙芯处理器展览。

龙芯(3)2005年1月31日举行了由中国科学院组织的龙芯2号鉴定会,2005年4月18日在北京人民大会堂召开了由科技部、中科院和信息产业部联合举办的龙芯2号发布会,人大常委会副委员长顾秀莲参加了龙芯2号发布会。

龙芯(3)2005年1月31日举行了由中国科学院组织的龙芯2号鉴定会,2005年4月18日在北京人民大会堂召开了由科技部、中科院和信息产业部联合举办的龙芯2号发布会,人大常委会副委员长顾秀莲参加了龙芯2号发布会。

2006年3月18日,龙芯2号增强型处理器CZ70流片成功。“龙芯” 也要对Intel说“不”了 (此说法有带广告宣传的性质)

2006年10月,中法两国在北京签署了关于中国科学院与意法半导体公司关于龙芯处理器的战略合作协议,中国国家主席胡锦涛与法国总统希拉克共同出席了协议的签字仪式。

2007年7月31日,龙芯2F(代号PLA80)流片成功,龙芯2F为龙芯第一款产品芯片。

2008年3月,北京龙芯中科技术服务中心有限公司正式成立,龙芯开始产业探索。

2009年9月28日,我国首款四核CPU龙芯3A(代号PRC60)流片成功。

2010年9月,龙芯大CPU系列的首款多核处理器产品——龙芯3A开始量产,中CPU系列的最新产品龙芯2G流片成功。龙芯2G在设计规格上相当于龙芯3A的单核版。与上一代龙芯2F相比,在二级缓存容量、IO总线带宽,配套桥片性能上都有大幅提升。龙芯2G在1GHz情况下运行稳定,可提供更好地用户体验,并适用于笔记本电脑与瘦客户机等移动与桌面市场。

2011年初,龙芯一号系列芯片家族中的新成员——龙芯1B芯片流片成功,龙芯1B是一款32位SoC芯片,片内集成32位处理器核、LCD显示接口、以及丰富的IO接口。该款芯片延续了龙芯处理器高性能、低功耗的优势,能够满足超低价位云终端、工业控制/数据采集、网络设备、消费类电子等领域需求。

2011年4月,龙芯3B流片成功。龙芯3B仍采用65纳米生产工艺,在单个芯片上集成8个增强型龙芯GS464处理器核,它可以与MIPS64兼容,并支持X86虚拟机和向量扩展。在1G主频下可实现128G flops的运算能力。在存储设计方面,龙芯3B最多可同时处理64个访问请求,可提供12.8GB/S的访存带宽。在I/O接口方面,龙芯3B实现2个16位的HyperTransport接口,可提供高达12.8GB/S的IO吞吐能力。八核龙芯3号的芯片对外接口与四核龙芯3号完全一致,两款芯片引脚完全兼容,可实现无缝更换。

2011年底,在国家核高基项目的支持下,龙芯历史上最为复杂,也是设计难度最高的一款芯片--龙芯2H流片成功。

2012年10月,龙芯3B 1500流片成功。处理器采用32纳米工艺,硅片面积160mm2。支持1.15v-1.3v变压,动态变频。实测核心频率1.3GHz - 1.5GHz,HT总线频率1600MHz,DDR3总线频率600MHz以上。龙芯3B 1500集成8核向量处理器,峰值运算能力可达192GFLOPS,功耗约为40w。每核配置两级私有256KB 缓存,所有核心共享片上三级缓存,总容量达8MB。支持双处理器通过HT总线直连构成16核CC-NUMA系统。龙芯3B 1500处理器结构及封装引脚基本兼容龙芯3B 1000。龙芯3A/3B使用的内核、操作系统及上层应用可支持龙芯3B 1500。

2013年4月,龙芯1C芯片[5]流片成功,龙芯1C芯片是基于LS232处理器核的高性价比单芯片系统,可应用于指纹生物识别、物联传感等领域。

2014年3月19日,龙芯1D芯片的量产版本(LS1D4)完成流片封装。龙芯1D是一款专门为超声波流量表应用而定制设计的数模混合SoC,片上集成了LS132处理器核、超声波时间测量、超声波脉冲发生器、温度测量单元、红外收发器、段式LCD控制器、A/D、空管检测单元、超声波换能器正常检测、模拟比较器等功能部件以及串口、液晶显示等接口。龙芯1D具有高精度、低功耗、低成本的特性,拥有广阔的市场前景。

2014年4月,龙芯公司推出了龙芯3B六核桌面解决方案。龙芯3B六核芯片是一个配置为六核的高性能通用处理器,采用32nm工艺制造,工作主频为1.2GHZ。该解决方案使用mini itx规格主板,板载AMD RS780E南桥芯片,配置1个千兆网络接口,另外具有PCI、PCIe、SATA、USB等多种外设接口,并且可配备hd6770独立显卡以及SSD硬盘等,具有良好的可扩展性。

2014年4月,龙芯公司推出了龙芯3B六核桌面解决方案。龙芯3B六核芯片是一个配置为六核的高性能通用处理器,采用32nm工艺制造,工作主频为1.2GHZ。该解决方案使用mini itx规格主板,板载AMD RS780E南桥芯片,配置1个千兆网络接口,另外具有PCI、PCIe、SATA、USB等多种外设接口,并且可配备hd6770独立显卡以及SSD硬盘等,具有良好的可扩展性。

2015年8月18日,龙芯中科正式发布其新一代处理器架构产品,包括自主指令集LoongISA、新一代处理器微结构GS464E、新一代处理器“龙芯3A2000”和“龙芯3B2000”、龙芯基础软硬件标准以及社区版操作系统LOONGNIX。[6]

众所周知,CPU是决定电脑性能的核心部件,也是整个系统的核心。其负责整个系统指令的执行、数学与逻辑的运算;数据的存储与传送;以及对内对外输入/输出的控制。而在这个电脑核心部件市场领域里,人们最为熟悉的两个品牌无疑是Intel和AMD,他们在处理器市场的强势地位似乎无人能撼动。在CPU技术上,我们跟国外厂商有着较大的差距,缺乏具有自主知识产权的CPU芯片,是中国计算机产业的一大“芯”病,也是我们这些电子工作者、网络人胸口永远的痛。

过去,代表着国际IT顶尖技术的CPU芯片一直被英特尔等国外巨头所垄断,中国企业及消费者为之付出了巨额版权费。好在神州龙芯公司先后推出了“龙芯1号”、“龙芯2号”,打破了中国无“芯”的历史。“龙芯”的诞生被业内人士誉为民族科技产业化道路上的一个里程碑。商品化的“龙芯”1号CPU的研制成功标志着中国已打破国外垄断,

初步掌握了当代CPU设计的关键技术,为改变中国信息产业“无芯”的局面迈出了重要的步伐,对中国形成有自主知识产权的计算机产业有重要的推动作用,对中国的CPU核心技术、国家安全、经济发展都有举足轻重的作用。我们有信心:“龙芯” 对Intel说“不” !

2019年12月24日,龙芯发布新一代处理器架构产品龙芯3A4000/3B4000处理器,龙芯3A4000依然采用28nm工艺,主频提升至1.8GHz-2.0GHz,内存升级为DDR4接口,同时支持动态调频调压。此外,统一操作系统UOS龙芯版也已适用龙芯3A3000系列、龙芯3B3000系列、3A4000系列、龙芯3B4000系列,全面适配龙芯桌面电脑、服务器。[7]

龙芯系列

龙芯一号

(英文名称Godson-1)

龙芯一号CPU IP核是兼顾通用及嵌入式CPU特点的32位处理器内核,采用类MIPS III指令集,具有七级流水线、32位整数单元和64位浮点单元。龙芯一号CPU IP核具有高度灵活的可配置性,方便集成的各种标准接口。图1显示了龙芯一号CPU IP核可配置结构,其中虚线部分表示用户可根据自己的需求进行选择配置,从而定制出最适合用户应用的处理器结构。主要的可配置模块包括:浮点部件、多媒体部件、内存管理、Cache、协处理器接口。浮点部件完全兼容MIPS的浮点指令集合,浮点部件及其相关的系统软件完全符合ANSI/IEEE 754-1985二进制浮点运算标准。浮点部件主要包括浮点ALU部件和浮点乘法/除法部件,用户可根据自己的实际应用选择是否添加。媒体部件复用了MIPS浮点指令的Format域,并复用了浮点寄存器堆,媒体指令集基本对应了Intel SSE媒体指令集合的各种操作。

内存管理部件有三种工作模式,即标准模式、直接映射模式和无映射模式。在标准模式下,TLB分为ITLB和DTLB两部分,每部分均由48项页表项组成,同时支持mapped和unmapped的从虚拟地址到物理地址的变换方式;TLB也可只进行直接映射,不使用CAM和RAM,以减小面积;而无映射模式下甚至可以去掉TLB,采用直连SRAM的形式实现访存。龙芯一号CPU IP核的Cache分为指令Cache和数据Cache,两部分独立配置,以4K为一路,可配置为4路、2路和0路。用户可根据应用需要,确定所需Cache的大小,甚至不使用Cache。协处理器接口为外部协处理器提供了一个高效率的接口。龙芯一号CPU IP核提供了两套可配置的处理器总线接口:AMBA接口和哈佛结构SRAM接口。

龙芯二号

(英文名称Godson-2)

(英文名称Godson-2)

龙芯二号CPU 采用先进的四发射超标量超流水结构,片内一级指令和数据高速缓存各64KB,片外二级高速缓存最多可达8MB.最高频率为1000MHz,功耗为3-5瓦,远远低于国外同类芯片,其SPEC CPU2000测试程序的实测性能是1.3GHz的威盛处理器的2-3倍,已达到中等Pentium4水平。

龙芯三号

(英文名称Godson-3)

龙芯3A的工作频率为900MHz~1GHz,功耗约15W,频率为1GHz时双精度浮点运算速度峰值达到每秒160亿次,单精度浮点运算速度峰值每秒320亿次。龙芯3A采用意法半导体公司(STMicro)65纳米CMOS工艺生产,晶体管数目达4.25亿个,芯片采用BGA封装,引脚的数目为1121个,功耗小于15瓦。 龙芯3A集成了四个64位超标量处理器核、4MB的二级Cache、两个DDR2/3内存控制器、两个高性能HyperTransport控制器、一个PCI/PCIX控制器以及LPC、SPI、UART、GPIO等低速I/O控制器。龙芯3A的指令系统与MIPS64兼容并通过指令扩展支持X86二进制翻译。

产品架构

架构

灵活的可配置IP核架构

Cache容量可配置

0/4K/8K/16K I/D Cache

TLB形式可配置

接口

可配置接口

AMBA 2.0 full compatible

龙芯Direct RAM (Harvard Structure)

龙芯Direct RAM (Harvard Structure)

MIPS SYSAD

Co-processor Intelface

内外时钟关系可配置

IEEE754兼容FPU可配置

MMX部件可配置

EJTAG接口,便于SOC调试

功耗

具体配置相关,Typical::1~2 mW/MHz

面积

与具体配置相关,Min:1.0mm2 (软IP)

友好的IP用户接口

可视化配置界面

完全可综合的IP,可无缝衔接主流EDA工具

集成synthesis环境

verilog仿真模型

IP Modeling

ISS仿真器

SoC硬件验证平台

SoC系统虚拟开发平台

软/硬IP

IP抽象模型提取,提供工业格式文件

硬IP的实现(0.18微米/0.13微米工艺)

IP架构

增强可配置灵活性

在面积、功耗上持续优化

针对应用不断增强处理能力(加密安全,控制,JAVA)

增加对多核的支持

SOC开发平台

提供基于EJTAG的IDE

提供ISS用于性能评估

系统

硬件开发板

操作系统

Linux

OpenBSD (N64 ABI)

VxWorks

WinCE

软件支持

软件支持

XFree86-4.1.0 X Server

Mozilla Browser,Apache WEB server

Compiler:GCC,F77

Word processing,video server

Virtual Terminal for X and Wind

产品介绍

龙芯1号

龙芯1号(英文名称Godson-1)于2002年研发完成,32位,主频 266 MHz。

龙芯1D

龙芯1D于2012年6月完成设计并进入流片状态,是专门为超声波热量表定制的高精度、低功耗测量SoC。

龙芯1D集成的时间数字转换器设计测量分辨率可达15ps,能够检测极其微小的流量变化。在电源管理方面,龙芯1D包含11个电源域,可将待机电流控制在10uA以下。测量过程的软硬件协同设计使得龙芯1D在热量表中用一个电池能工作五年以上。

除了热量表,龙芯1D还可以应用在水表、激光测距、重量测量等场合,是一个非常值得期待的产品。

最初版本

龙芯2号(英文名称Godson-2)于2003年正式完成并发布。

龙芯2号是64位处理器,主频为300MHz至1000MHz,500MHz版约与1GHz版的Intel Pentium III、Pentium 4拥有相近的效能水平。

龙芯2号最初的版本是用0.13微米工艺,往后也会使用更精细的工艺。事实上龙芯2号当称为一个系列,过程中经过数次改进,已知的有2、2A、2B、2C、2E、2F等型号,龙芯2号处理器已用于黄羊河公司(YellowSheepRiver,简称:YSR)的低价型Linux台式机:Municator中,最初的售价约为1200元人民币。其电脑皆曾在2006 年3月德国汉诺威CeBIT及6月的台北国际电脑展览会中展出。

龙芯2E

2006年6月,龙芯2E继成功在法国流片成功后,全世界排名第五位的集成电路生产商--意法半导体公司与中科院计算所签订技术许可协议,购买龙芯2E的生产和全球销售权。意法半导体计划每年销售龙芯芯片1000万片以上。

2006年9月13日,中国科学家宣布研制成功通用中央处理器芯片龙芯2E。它是一款采用64位MIPSⅢ指令集的RISC处理器,采用90纳米的CMOS工艺,晶体管数目是4700万个,芯片面积是6.8mm×5.2mm。最高主频达到1.0GHz,一般频率是800MHz,功耗大约是5-7瓦。实际运行频率定于660MHz。规格方面,龙芯2E处理器有128KB一级缓存、512KB二级缓存。性能方面,它的单精度浮点运算速度是每秒80亿次,双精度浮点运算速度是每秒40亿次。龙芯2E在1.0GHz主频下,SPEC CPU2000的得分为500分,综合性能达到Pentium III和Pentium 4的水平。

龙芯2F

龙芯2F与龙芯2E相比,主要有以下几个方面的提高。一是主频提高30%以上,通过频率筛选,将有1GHz以上的产品。二是相同频率下功耗降低40%左右,并增加了很多诸如降频、温度传感器、关闭L2等功耗管理功能。三是集成了更多的系统功能,除了CPU外,还集成了DDR2内存控制器、66MHz PCI/100MHz PCIX控制器、Local IO控制器、GPIO、中断控制器、DMA控制器、部分显示加速等功能,将大幅度降低系统成本。四是封装更小,龙芯2E的封装为35mm*35mm,龙芯2F为27mm*27mm。五是可测性设计(DFT)和可生产性设计(DFM)有明显提高,因此可以降低芯片成本。

龙芯2G

龙芯2G在设计规格上相当于龙芯3A的单核版。与上一代龙芯2F相比,在二级缓存容量、IO总线带宽,配套桥片性能上都有大幅提升。龙芯2G在1GHz情况下运行稳定,可提供更好地用户体验,并适用于笔记本电脑与瘦客户机等移动与桌面市场。

龙芯2H

龙芯2H已于2012年底完成了流片,64nm工艺,它在一个芯片中集成了CPU,GPU,北桥芯片,南桥芯片,内存控制器,显卡,网卡,声卡,USB模块等各种IO接口。芯片高度SOC设计,最大功耗为4W,主频1GHz,是龙芯家族中集成度最高的芯片。主要面向移动终端,笔记本电脑,平板电脑等移动处理器。

龙芯3A

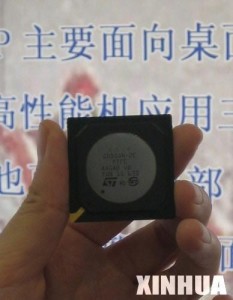

龙芯L3A02中国第一个具有完全自主知识产权的四核CPU,龙芯3号处理器采用的是65nm(纳米)工艺,主频1GHz,晶体管数目4.25亿个, 单颗龙芯3A的最大功耗为15W,理论峰值为16Gflops,每颗CPU单瓦特能效比1.06Gflops/W是X86 CPU的2倍以上,达到了世界先进水平。龙芯3号多核CPU系列产品定位服务器和高性能计算机应用。

龙芯L3A02中国第一个具有完全自主知识产权的四核CPU,龙芯3号处理器采用的是65nm(纳米)工艺,主频1GHz,晶体管数目4.25亿个, 单颗龙芯3A的最大功耗为15W,理论峰值为16Gflops,每颗CPU单瓦特能效比1.06Gflops/W是X86 CPU的2倍以上,达到了世界先进水平。龙芯3号多核CPU系列产品定位服务器和高性能计算机应用。

龙芯3A集成了四个64位超标量处理器核、4MB的二级Cache、两个DDR2/3内存控制器、两个高性能HyperTransport控制器、一个PCI/PCIX控制器以及LPC、SPI、UART、GPIO等低速I/O控制器。龙芯3A的指令系统与MIPS64兼容并通过指令扩展支持X86二进制翻译。

龙芯3B

继龙芯3A后,龙芯3号系列处理器的第二代产品——8核龙芯3B处理器已于2012年年初流片成功。龙芯公司相关部门正在对该款芯片做进一步的开发和测试工作。预计2012年夏天实现量产。

龙芯3B仍采用65纳米生产工艺,在单个芯片上集成8个增强型龙芯GS464处理器核,它可以与MIPS64兼容,并支持X86虚拟机和向量扩展。在1G主频下可实现128G flops的运算能力。在存储设计方面,龙芯3B最多可同时处理64个访问请求,可提供12.8GB/S的访存带宽。在I/O接口方面,龙芯3B实现2个16位的HyperTransport接口,可提供高达12.8GB/S的IO吞吐能力。八核龙芯3号的芯片对外接口与四核龙芯3号完全一致,两款芯片引脚完全兼容,可实现无缝更换。

我国首台采用自主设计的“龙芯3B”八核处理器的万亿次高性能计算机“KD-90”,由中国科学技术大学与深圳大学联合研制成功。

高性能计算机KD-90采用单一机箱,集成了10颗八核龙芯3B处理器,理论峰值计算能力达到每秒1万亿次。系统硬件由1个前置服务器、5个计算节点、2个千兆以太网交换机以及监控单元组成。其中,前置服务器和计算节点均采用了我国自主设计的龙芯3B八核处理器,主要互连部件采用了自主研发的超多端口千兆以太网交换芯片。系统软件以开源软件为主,其中包括针对龙芯3B处理器结构专门优化的数学函数库,以及自主研发的图形化系统监控管理软件,具有兼容性强、易维护、易升级、易使用等特点。

KD-90的研制依托国家科技重大专项“高性能多核CPU研发与应用”项目的支持,由中科院院士、中国科技大学教授陈国良为负责人的科研团队,历时近一年攻关成功。与基上一代“龙芯”处理器的国产高性能计算机KD-60相比,KD-90系统实现了“三低一高”的特性:成本低于20万元,功耗低于900W,体积降低至0.12平方米,性能高达每秒1万亿次。

以中科院院士陆汝钤为组长的专家组鉴定后认为,KD-90是我国高性能计算机国产化的又一次重要突破,在编程模型和互联网络等关键技术上达到了世界先进水平。适用于高性能计算教学、大规模科学与工程计算,以及军事科学、国家安全和国民经济建设等领域,应用前景广阔。

龙芯3B1500

3B 1500在核高基项目支持下,龙芯3B 1500处理器流片成功。龙芯3B 1500集成8核向量处理器,32纳米工艺,主频1.3—1.5GHz,硅片面积182.5mm2,支持1.15v-1.3v变压和动态变频。龙芯3B 1500结构及封装引脚基本兼容龙芯3B 1000,性能较龙芯四核3A处理器大幅提升。龙芯3B 1500流片成功,标志着核高基支持任务的技术指标全面完成。[8]

3B 1500在核高基项目支持下,龙芯3B 1500处理器流片成功。龙芯3B 1500集成8核向量处理器,32纳米工艺,主频1.3—1.5GHz,硅片面积182.5mm2,支持1.15v-1.3v变压和动态变频。龙芯3B 1500结构及封装引脚基本兼容龙芯3B 1000,性能较龙芯四核3A处理器大幅提升。龙芯3B 1500流片成功,标志着核高基支持任务的技术指标全面完成。[8]

龙芯规格

龙芯1A

| 主频 | 300MHz |

| 微体系结构 | 集成32位超标量处理器核,该处理器核具有如下特点:支持MIPS 32指令集;5级流水线结构;双发射乱序执行结构;1个定点单元、1个浮点单元和1个访存单元;采用交叉开关和多级AMBA总线桥进行片内的互连 |

| 高速缓存 | 一级指令cache和数据cache各16KB |

| 内存控制器 | 1个32 /16位DDR2-333控制器 |

| 音视频 | 支持1920*1080/60fps的LCD+VGA控制器;AC97音频控制器;333控制器 |

| I/O | USB2.0/1.1 *4;SATA2*2;GMAC*2;PCI Host/Device、 LPC、I2C、CAN;SPI、NAND;UART*4、RTC、PWM、GPIO*88 等I/O控制器 |

| 制造工艺 | 130nm CMOS工艺 |

| 封装 | 23mm*23mm BGA封装,448个引脚 |

| 功耗 | 1.0W;支持动态电源管理 |

龙芯1B

| 主频 | 200MHz |

| 微体系结构 | 集成32位超标量处理器核,该处理器核具有如下特点:支持MIPS 32指令集;5级流水线结构;双发射乱序执行结构;1个定点单元和1个访存单元;采用交叉开关和多级AMBA总线桥进行片内的互连 |

| 高速缓存 | 一级指令cache和数据cache各8KB |

| 内存控制器 | 1个32 /16位DDR2-266控制器 |

| 音视频 | 支持1920*1080/60fps的LCD控制器;AC97音频控制器 |

| I/O | USB2.0/1.1 *1;GMAC*2;I2C、CAN;SPI、NAND;UART*12、RTC、PWM、GPIO*62 等I/O控制器 |

| 制造工艺 | 130nm CMOS工艺 |

| 封装 | 17mm*17mm BGA封装,256个引脚 |

| 功耗 | <0.5W |

龙芯2F

| 主频 | 800MHz |

| 微体系结构 | 集成64位超标量处理器核,该处理器核具有如下特点:支持MIPS III指令集;9级超流水线结构;四发射乱序执行结构;2个定点单元、2个浮点单元和1个访存单元 |

| 高速缓存 | 一级指令cache和数据cache各64KB;二级cache 512KB |

| 内存控制器 | 集成72位DDR1/2-667控制器,支持ECC校验 |

| 高速I/O | 无 |

| 其它I/O | 集成PCI、Local IO、GPIO等I/O控制器 |

| 制造工艺 | 90nm CMOS工艺 |

| 封装 | 27mm*27mm BGA封装,452个引脚 |

| 功耗 | <5W@800MHz支持动态降频 |

龙芯2G

| 主频 | 900MHz-1GHz |

| 微体系结构 | 集成3-4个64位超标量处理器核,每个处理器核具有如下特点:支持MIPS64指令集及龙芯扩展指令集;9级超流水线结构;四发射乱序执行结构;2个定点单元、2个浮点单元和1个访存单元;采用交叉开关进行核间互连 |

| 高速缓存 | 每个处理器核的一级指令cache和数据cache各64KB多个处理器核通过交叉开关共享4MB的二级cache |

| 内存控制器 | 集成两个64位DDR2/3-800控制器 |

| 高速I/O | 集成一个HyperTransport控制器,带宽达到6.4GB/s |

| 其它I/O | 集成LPC、SPI、UART、GPIO等I/O控制器 |

| 制造工艺 | 65nm CMOS工艺 |

| 封装 | 31mm*31mm BGA封装,741个引脚 |

| 功耗 | <15W@1GHz支持动态降频 |

龙芯3A

| 主频 | 1GHz |

| 微体系结构 | 集成4个64位超标量处理器核,每个处理器核具有如下特点:支持MIPS64指令集及龙芯扩展指令集;9级超流水线结构;四发射乱序执行结构;2个定点单元、2个浮点单元和1个访存单元;采用交叉开关进行核间互连;通过HT接口进行片间可伸缩互连 |

| 高速缓存 | 每个处理器核的一级指令cache和数据cache各64KB四个处理器核通过交叉开关共享4MB的二级cache |

| 内存控制器 | 集成两个72位DDR2/3-800控制器,支持ECC校验 |

| 高速I/O | 集成两个HyperTransport控制器,带宽达到12.8GB/s,支持两个处理器无缝互连 |

| 其它I/O | 集成PCI控制器以及LPC、SPI、UART、GPIO等I/O控制器 |

| 制造工艺 | 65nm CMOS工艺 |

| 封装 | 40mm*40mm BGA封装,1121个引脚,与龙芯3B引脚兼容 |

| 功耗 | <15W@1GHz支持动态降频 |

龙芯3B

龙芯3B主要用于高性能计算机、高性能服务器、数字信号处理等领域。

| 主频 | 1GHz |

| 微体系结构 | 集成8个64位超标量处理器核,每个处理器核具有如下特点:支持MIPS64指令集及龙芯扩展指令集;9级超流水线结构;四发射乱序执行结构;2个定点单元、2个浮点单元和1个访存单元;每个浮点单元支持256位向量运算;采用交叉开关进行核间互连;通过HT接口进行片间可伸缩互连 |

| 高速缓存 | 每个处理器核的一级指令cache和数据cache各64KB八个处理器核通过交叉开关共享4MB的二级cache |

| 内存控制器 | 集成两个DDR2/3-800控制器 |

| 高速I/O | 集成两个HyperTransport控制器,带宽达到12.8GB/s,支持多个处理器无缝互连 |

| 其它I/O | 集成PCI控制器以及LPC、SPI、UART、GPIO等I/O控制器 |

| 制造工艺 | 65nm CMOS工艺 |

| 封装 | 40mm*40mm BGA封装,1121个引脚,与龙芯3A引脚兼容 |

| 功耗 | <50W@1GHz支持动态降频 |

龙芯3B1500

龙芯3B1500是国产商用32纳米8核处理器,最高主频可达1.5GHz,支持向量运算加速,最高峰值计算能力达到192GFLOPS,具有很高的性能功耗比。龙芯3B1500主要用于高端桌面计算机、高性能计算机、高性能服务器、数字信号处理等领域。

| 主频 | 1.2GHz-1.5GHz |

| 微体系结构 | 集成8个64位超标量处理器核,每个处理器核具有如下特点: 支持MIPS64指令集及龙芯扩展指令集; 9级超流水线结构; 四发射乱序执行结构; 2个定点单元、2个浮点单元和1个访存单元; 每个浮点单元支持256位向量运算; 采用交叉开关进行核间互连; 通过HT接口进行片间可伸缩互连 |

| 高速缓存 | 64KB私有一级指令cache和数据cache 128KB私有二级cache 8个处理器核共享8MB的三级cache |

| 内存控制器 | 集成两个72位DDR2/3控制器,支持ECC校验 |

| 高速I/O | 集成两个HyperTransport2.0控制器 |

| 其它I/O | 集成PCI控制器以及LPC、SPI、UART、GPIO等I/O控制器 |

| 制造工艺 | 32nm CMOS工艺 |

| 封装 | 40mm*40mm BGA封装,1121个引脚,与龙芯3A功能引脚兼容,电源引脚部分有差异 |

| 功耗 | 30W@1.2GHz典型工作模式 40W@1GHz向量工作模式 |

衍生产品

| 主频 | 300MHz |

| 微体系结构 | 集成32位超标量处理器核,该处理器核具有如下特点:支持MIPS 32指令集;5级流水线结构;双发射乱序执行结构;1个定点单元、1个浮点单元和1个访存单元;采用交叉开关和多级AMBA总线桥进行片内的互连 |

| 高速缓存 | 一级指令cache和数据cache各16KB |

| 内存控制器 | 1个32 /16位DDR2-333控制器 |

| 音视频 | 支持1920*1080/60fps的LCD+VGA控制器;AC97音频控制器;333控制器 |

| I/O | USB2.0/1.1 *4;SATA2*2;GMAC*2;PCI Host/Device、 LPC、I2C、CAN;SPI、NAND;UART*4、RTC、PWM、GPIO*88 等I/O控制器 |

| 制造工艺 | 130nm CMOS工艺 |

| 封装 | 23mm*23mm BGA封装,448个引脚 |

| 功耗 | 1.0W;支持动态电源管理 |

迷你计算机

| 主频 | 200MHz |

| 微体系结构 | 集成32位超标量处理器核,该处理器核具有如下特点:支持MIPS 32指令集;5级流水线结构;双发射乱序执行结构;1个定点单元和1个访存单元;采用交叉开关和多级AMBA总线桥进行片内的互连 |

| 高速缓存 | 一级指令cache和数据cache各8KB |

| 内存控制器 | 1个32 /16位DDR2-266控制器 |

| 音视频 | 支持1920*1080/60fps的LCD控制器;AC97音频控制器 |

| I/O | USB2.0/1.1 *1;GMAC*2;I2C、CAN;SPI、NAND;UART*12、RTC、PWM、GPIO*62 等I/O控制器 |

| 制造工艺 | 130nm CMOS工艺 |

| 封装 | 17mm*17mm BGA封装,256个引脚 |

| 功耗 | <0.5W |

迷你笔记本

| 主频 | 800MHz |

| 微体系结构 | 集成64位超标量处理器核,该处理器核具有如下特点:支持MIPS III指令集;9级超流水线结构;四发射乱序执行结构;2个定点单元、2个浮点单元和1个访存单元 |

| 高速缓存 | 一级指令cache和数据cache各64KB;二级cache 512KB |

| 内存控制器 | 集成72位DDR1/2-667控制器,支持ECC校验 |

| 高速I/O | 无 |

| 其它I/O | 集成PCI、Local IO、GPIO等I/O控制器 |

| 制造工艺 | 90nm CMOS工艺 |

| 封装 | 27mm*27mm BGA封装,452个引脚 |

| 功耗 | <5W@800MHz支持动态降频 |

便携式笔记本

| 主频 | 900MHz-1GHz |

| 微体系结构 | 集成3-4个64位超标量处理器核,每个处理器核具有如下特点:支持MIPS64指令集及龙芯扩展指令集;9级超流水线结构;四发射乱序执行结构;2个定点单元、2个浮点单元和1个访存单元;采用交叉开关进行核间互连 |

| 高速缓存 | 每个处理器核的一级指令cache和数据cache各64KB多个处理器核通过交叉开关共享4MB的二级cache |

| 内存控制器 | 集成两个64位DDR2/3-800控制器 |

| 高速I/O | 集成一个HyperTransport控制器,带宽达到6.4GB/s |

| 其它I/O | 集成LPC、SPI、UART、GPIO等I/O控制器 |

| 制造工艺 | 65nm CMOS工艺 |

| 封装 | 31mm*31mm BGA封装,741个引脚 |

| 功耗 | <15W@1GHz支持动态降频 |

开发板

| 主频 | 1GHz |

| 微体系结构 | 集成4个64位超标量处理器核,每个处理器核具有如下特点:支持MIPS64指令集及龙芯扩展指令集;9级超流水线结构;四发射乱序执行结构;2个定点单元、2个浮点单元和1个访存单元;采用交叉开关进行核间互连;通过HT接口进行片间可伸缩互连 |

| 高速缓存 | 每个处理器核的一级指令cache和数据cache各64KB四个处理器核通过交叉开关共享4MB的二级cache |

| 内存控制器 | 集成两个72位DDR2/3-800控制器,支持ECC校验 |

| 高速I/O | 集成两个HyperTransport控制器,带宽达到12.8GB/s,支持两个处理器无缝互连 |

| 其它I/O | 集成PCI控制器以及LPC、SPI、UART、GPIO等I/O控制器 |

| 制造工艺 | 65nm CMOS工艺 |

| 封装 | 40mm*40mm BGA封装,1121个引脚,与龙芯3B引脚兼容 |

| 功耗 | <15W@1GHz支持动态降频 |

产品意义

| 主频 | 1GHz |

| 微体系结构 | 集成8个64位超标量处理器核,每个处理器核具有如下特点:支持MIPS64指令集及龙芯扩展指令集;9级超流水线结构;四发射乱序执行结构;2个定点单元、2个浮点单元和1个访存单元;每个浮点单元支持256位向量运算;采用交叉开关进行核间互连;通过HT接口进行片间可伸缩互连 |

| 高速缓存 | 每个处理器核的一级指令cache和数据cache各64KB八个处理器核通过交叉开关共享4MB的二级cache |

| 内存控制器 | 集成两个DDR2/3-800控制器 |

| 高速I/O | 集成两个HyperTransport控制器,带宽达到12.8GB/s,支持多个处理器无缝互连 |

| 其它I/O | 集成PCI控制器以及LPC、SPI、UART、GPIO等I/O控制器 |

| 制造工艺 | 65nm CMOS工艺 |

| 封装 | 40mm*40mm BGA封装,1121个引脚,与龙芯3A引脚兼容 |

| 功耗 | <50W@1GHz支持动态降频 |

研发经过

| 主频 | 1.2GHz-1.5GHz |

| 微体系结构 | 集成8个64位超标量处理器核,每个处理器核具有如下特点: 支持MIPS64指令集及龙芯扩展指令集; 9级超流水线结构; 四发射乱序执行结构; 2个定点单元、2个浮点单元和1个访存单元; 每个浮点单元支持256位向量运算; 采用交叉开关进行核间互连; 通过HT接口进行片间可伸缩互连 |

| 高速缓存 | 64KB私有一级指令cache和数据cache 128KB私有二级cache 8个处理器核共享8MB的三级cache |

| 内存控制器 | 集成两个72位DDR2/3控制器,支持ECC校验 |

| 高速I/O | 集成两个HyperTransport2.0控制器 |

| 其它I/O | 集成PCI控制器以及LPC、SPI、UART、GPIO等I/O控制器 |

| 制造工艺 | 32nm CMOS工艺 |

| 封装 | 40mm*40mm BGA封装,1121个引脚,与龙芯3A功能引脚兼容,电源引脚部分有差异 |

| 功耗 | 30W@1.2GHz典型工作模式 40W@1GHz向量工作模式 |

未来展望

词条图册

福珑2E迷你电脑:基于国产龙芯处理器的这种主机尺寸不到普通PC的十分之一,仅与普通电脑光驱相当。采用中科院计算所研制的龙芯-2E处理器(主频:666MHz),默认配有256M内存,40G的笔记本硬盘,ATI RADEON 7000-M。在接口方面,福珑迷你电脑也比较齐备,配备有显示器和COM接口,音频输入输出接口,一个用于连接鼠标或键盘的PS2口,以及4个USB接口,可满足常用外设的接入。此外,福珑迷你电脑还配有台式机不常见的红外线接口和可输出到电视机的S端子,可通过内置的软件,使用遥控器操作在电视上播放媒体文件,其功能相当于普通机顶盒。考虑到体积的因素,此款电脑没有预置光驱,但用户可选配USB光驱。[9]

福珑2E迷你电脑:基于国产龙芯处理器的这种主机尺寸不到普通PC的十分之一,仅与普通电脑光驱相当。采用中科院计算所研制的龙芯-2E处理器(主频:666MHz),默认配有256M内存,40G的笔记本硬盘,ATI RADEON 7000-M。在接口方面,福珑迷你电脑也比较齐备,配备有显示器和COM接口,音频输入输出接口,一个用于连接鼠标或键盘的PS2口,以及4个USB接口,可满足常用外设的接入。此外,福珑迷你电脑还配有台式机不常见的红外线接口和可输出到电视机的S端子,可通过内置的软件,使用遥控器操作在电视上播放媒体文件,其功能相当于普通机顶盒。考虑到体积的因素,此款电脑没有预置光驱,但用户可选配USB光驱。[9]

小巧玲珑的龙芯II福珑迷你电脑,而这台电脑满负载功率也不超过20W。搭配可自由定制的开源Linux操作系统。

福珑2F迷你电脑:采用全金属外壳机箱,设计新颖且小巧轻便。内置我国拥有自主知识产权的龙芯2F高性能处理器,并搭配可自由定制的开源Linux操作系统。福珑2F迷你电脑2F6003,内置64位低功耗新一代龙芯2F处理器。据中科龙梦知情人士透露,此次推出的福珑2F迷你电脑为此前2F6002的升级版,增加了一些DVI接口。2F6002曾于4月15日上市,官方指导价为每台1800元。[10]

福珑2F迷你电脑:采用全金属外壳机箱,设计新颖且小巧轻便。内置我国拥有自主知识产权的龙芯2F高性能处理器,并搭配可自由定制的开源Linux操作系统。福珑2F迷你电脑2F6003,内置64位低功耗新一代龙芯2F处理器。据中科龙梦知情人士透露,此次推出的福珑2F迷你电脑为此前2F6002的升级版,增加了一些DVI接口。2F6002曾于4月15日上市,官方指导价为每台1800元。[10]

-

北京龙芯中科技术服务中心有限公司

2025-09-21 08:15:31 查看详情

求购

求购